News Release 14-125

Protecting our processors

NSF and SRC announce research awards to 10 universities to develop secure, trustworthy, assured and resilient semiconductors and systems

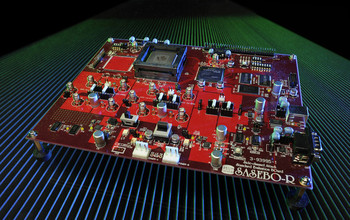

A side-channel attack evaluation board (SASEBO) used for tamper resistance research.

September 23, 2014

This material is available primarily for archival purposes. Telephone numbers or other contact information may be out of date; please see current contact information at media contacts.

The National Science Foundation (NSF) and Semiconductor Research Corporation (SRC) today announced nine research awards to 10 universities totaling nearly $4 million under a joint program focused on Secure, Trustworthy, Assured and Resilient Semiconductors and Systems (STARSS).

The awards support research at the circuit, architecture and system levels on new strategies, methods and tools to decrease the likelihood of unintended behavior or access; increase resistance and resilience to tampering; and improve the ability to provide authentication throughout the supply chain and in the field.

"The processes and tools used to design and manufacture semiconductors ensure that the resulting product does what it is supposed to do. However, a key question that must also be addressed is whether the product does anything else, such as behaving in ways that are unintended or malicious," said Keith Marzullo, division director of NSF's Computer and Network Systems Division, which leads the NSF/SRC partnership on STARSS. "Through this partnership with SRC, we are pleased to focus on hardware and systems security research addressing this challenge and to provide a unique opportunity to facilitate the transition of this research into practical use."

NSF's involvement in STARSS is part of its Secure and Trustworthy Cyberspace (SaTC) portfolio, which in August announced nearly $75 million in cybersecurity awards.

The STARRS program expands SRC's Trustworthy and Secure Semiconductors and Systems (T3S) program, engaging 10 universities across the U.S. Initial T3S industry participants are Freescale, Intel Corporation and Mentor Graphics. NSF is the first federal partner.

"The goal of SRC's T3S initiative is to develop cost-effective strategies and tools for the design and manufacture of chips and systems that are reliable, trustworthy and secure," said Celia Merzbacher, SRC vice president for innovative partnerships. "This includes designing for security and assurance at the outset so as to build in resistance and resilience to attack or tampering. The research enabled by the STARSS program with NSF is a cornerstone of this overall effort."

SRC is the world's leading university-research consortium for semiconductors and related technologies.

A number of trends are motivating industry and government to support research in hardware and system security. The design and manufacture of semiconductor circuits and systems requires many steps and involves the work of hundreds of engineers--typically distributed across multiple locations and organizations worldwide.

Moreover, a typical microprocessor is likely to include dozens of design modules from various sources. Designers at each level need assurance that the components being incorporated can be trusted in order for the final system to be trustworthy.

Today, the design and manufacture of semiconductor circuits and systems includes extensive verification and testing to ensure the final product does what it is intended to do. Similar approaches are needed to provide assurance that the product is authentic and does not allow unwanted functionality, access or control. This includes strategies, tools and methods at all stages, from architecture through manufacture and throughout the lifecycle of the product.

The first round of awards made through the STARSS program will support nine research projects with diverse areas of focus. They are:

- Combating integrated circuit counterfeiting using secure chip odometers--Carnegie Mellon University researchers will design and implement secure chip odometers to provide integrated circuits (ICs) with both a secure gauge of use/age and an authentication of provenance to detect counterfeit ICs;

- Intellectual Property (IP) Trust-A comprehensive framework for IP integrity validation--Case Western Reserve University and University of Florida researchers will develop a comprehensive and scalable framework for IP trust analysis and verification by evaluating IPs of diverse types and forms and develop threat models, taxonomy and instances of IP trust/integrity issues;

- Design of low-cost, memory-based security primitives and techniques for high-volume products--University of Connecticut researchers will develop metrics and algorithms to make static RAM physical "unclonable" functions that are substantially more reliable at extreme operating conditions and aging, and extend this to dynamic RAM and Flash;

- Trojan detection and diagnosis in mixed-signal systems using on-the-fly learned, pre-computed and side channel tests--Georgia Institute of Technology researchers will leverage knowledge of state of the art mixed-signal/analog/radio frequency for detection of Trojans in generic mixed-signal systems;

- Metric and CAD for differential power analysis (DPA) resistance--Iowa State University researchers will investigate statistical metrics and design techniques to measure and defend against DPA attacks;

- Design of secure and anti-counterfeit integrated circuits--University of Minnesota researchers will develop hierarchical approaches for authentication and obfuscation of chips;

- Hardware authentication through high-capacity, physical unclonable functions (PUF)-based secret key generation and lattice coding--University of Texas at Austin researchers will develop strong machine-learning resistant PUFs, capable of producing high-entropy outputs, and a new lattice-based stability algorithm for high-capacity secret key generation;

- Fault-attack awareness using microprocessor enhancements--Virginia Tech researchers will develop a collection of hardware techniques for microprocessor architectures to detect fault injection attacks, and to mitigate fault analysis through an appropriate response in software; and

- Invariant carrying machine for hardware assurance--Northwestern University researchers will develop techniques for improving the reliability and trustworthiness of hardware systems via an Invariant-Carrying Machine approach.

A second joint NSF-SRC STARSS funding opportunity was announced on Aug. 13 as part of the latest NSF SaTC program solicitation. For more information, visit the NSF website.

-NSF-

-

Scientists test and validate DC-DC converter chips in the laboratory.

Credit and Larger Version

Media Contacts

Aaron Dubrow, NSF, (703) 292-4489, email: adubrow@nsf.gov

Dan Francisco, SRC, (916) 812-8814, email: dan@integrityglobal.biz

Program Contacts

Nina Amla, NSF, (703) 292-8910, email: namla@nsf.gov

Related Websites

Semiconductor Research Corporation: https://www.src.org/

Secure and Trustworthy Cyberspace: Secure, Trustworthy, Assured and Resilient Semiconductors and Systems: http://www.nsf.gov/pubs/2014/nsf14528/nsf14528.htm

The U.S. National Science Foundation propels the nation forward by advancing fundamental research in all fields of science and engineering. NSF supports research and people by providing facilities, instruments and funding to support their ingenuity and sustain the U.S. as a global leader in research and innovation. With a fiscal year 2023 budget of $9.5 billion, NSF funds reach all 50 states through grants to nearly 2,000 colleges, universities and institutions. Each year, NSF receives more than 40,000 competitive proposals and makes about 11,000 new awards. Those awards include support for cooperative research with industry, Arctic and Antarctic research and operations, and U.S. participation in international scientific efforts.

Connect with us online

NSF website: nsf.gov

NSF News: nsf.gov/news

For News Media: nsf.gov/news/newsroom

Statistics: nsf.gov/statistics/

Awards database: nsf.gov/awardsearch/

Follow us on social

Twitter: twitter.com/NSF

Facebook: facebook.com/US.NSF

Instagram: instagram.com/nsfgov